|

|

本人是新手,正在学习DE2_70_TV例程,有些地方没看懂,希望各位高手出手相助。

在DE2_70_TV中用到的Sdram_Control_4Port模块:

- // SDRAM frame buffer

- Sdram_Control_4Port u6 ( // HOST Side

- .REF_CLK(iTD1_CLK27),

- .CLK_18(AUD_CTRL_CLK),

- .RESET_N(1'b1),

- // FIFO Write Side 1

- .WR1_DATA(YCbCr),

- .WR1(TV_DVAL),

- .WR1_FULL(WR1_FULL),

- .WR1_ADDR(0),

- .WR1_MAX_ADDR(640*507), // 525-18

- .WR1_LENGTH(9'h80),

- .WR1_LOAD(!DLY0),

- .WR1_CLK(iTD1_CLK27),

- // FIFO Read Side 1

- .RD1_DATA(m1YCbCr),

- .RD1(m1VGA_Read),

- .RD1_ADDR(640*13), // Read odd field and bypess blanking

- .RD1_MAX_ADDR(640*253),

- .RD1_LENGTH(9'h80),

- .RD1_LOAD(!DLY0),

- .RD1_CLK(iTD1_CLK27),

- // FIFO Read Side 2

- .RD2_DATA(m2YCbCr),

- .RD2(m2VGA_Read),

- .RD2_ADDR(640*267), // Read even field and bypess blanking

- .RD2_MAX_ADDR(640*507),

- .RD2_LENGTH(9'h80),

- .RD2_LOAD(!DLY0),

- .RD2_CLK(iTD1_CLK27),

- // SDRAM Side

- .SA(oDRAM0_A),

- .BA({oDRAM0_BA[1],oDRAM0_BA[0]}),

- .CS_N(oDRAM0_CS_N),

- .CKE(oDRAM0_CKE),

- .RAS_N(oDRAM0_RAS_N),

- .CAS_N(oDRAM0_CAS_N),

- .WE_N(oDRAM0_WE_N),

- .DQ(DRAM_DQ),

- .DQM({oDRAM0_UDQM1,oDRAM0_LDQM0}),

- .SDR_CLK(oDRAM0_CLK) );

另外,

“.RD1_ADDR(640*13), //Read odd field and bypess blanking

.RD1_MAX_ADDR(640*253), ”

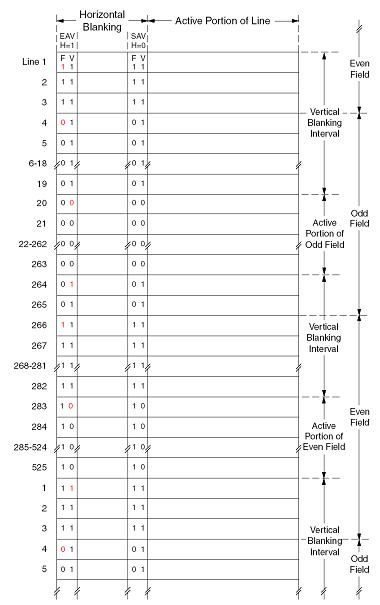

奇场是存放在13~253行吗?根据ITU656协议(下图),奇场不是应该存放在20~263行的吗?

希望能得到大家的帮助,小弟感激不尽! |

|